# Stream User's Guide

This User's Guide gives an introduction to Stream programming and to the use of Stream tools. It describes how to install the Stream toolset. It presents an overview of SPI stream processors, the Stream programming model, and the software development tools used to compile, simulate, run, and debug Stream programs. It gives a detailed tutorial introduction to the design and implementation of an application program using a concrete programming example.

#### SWUG-00001-007

This document contains confidential and proprietary information of Stream Processors, Inc. Possession of this document or any part thereof in any form constitutes full acceptance of the terms and conditions of the mutual Non-Disclosure Agreement in effect between the recipient and Stream Processors, Inc. The contents of this document are preliminary and subject to change without notice. The stream processing technology and other technologies described in this document are subject to issued patents and pending patent applications in the United States and other countries. This document confers upon recipient no right or license to make, have made, use, sell, or practice any of the technology or inventions described herein.

## Stream Processors, Inc.

455 DeGuigne Drive Sunnyvale, CA 94085-3890 USA Telephone: +1.408.616.3338

Fax: +1.408.616.3337

Email: <u>info@streamprocessors.com</u>

Web: <u>www.streamprocessors.com</u>

© 2005-2009 by Stream Processors, Inc. All rights reserved. This document contains advance information on SPI products, some of which are in development, sampling or initial production phases. The information and specifications contained herein are preliminary and are subject to change at the discretion of Stream Processors, Inc.

# **Table of Contents**

| 1 |          | ıction                                 |    |

|---|----------|----------------------------------------|----|

|   | 1.1 Typ  | pographical conventions                | 7  |

|   | 1.2 Do   | cument revision history                | 7  |

| 2 | Installa | tion                                   | 8  |

|   | 2.1 Inst | tall the toolset                       | 8  |

|   | 2.2 Dis  | tribution contents                     | 9  |

| 3 | Stream   | Programming                            | 10 |

|   | 3.1 Stre | eam programming model                  | 11 |

|   | 3.2 Stre | eam language extensions                | 11 |

|   | 3.2.1    | Added keywords                         | 11 |

|   | 3.2.2    | Predefined macros                      | 12 |

|   | 3.2.3    | Types                                  | 12 |

| 4 | Compo    | nent API                               | 13 |

|   | 4.1 Bas  | sics                                   | 13 |

|   | 4.1.1    | Components                             | 13 |

|   | 4.1.2    | Buffers                                | 14 |

|   | 4.1.3    | Ports                                  | 15 |

|   | 4.1.4    | Connections                            |    |

|   | 4.1.5    | Commands and responses                 | 16 |

|   | 4.2 Exe  | ecution                                | 18 |

|   | 4.2.1    | Component instance states              | 18 |

|   | 4.2.2    | Execution requirements                 |    |

|   | 4.2.3    | Scheduling priorities                  |    |

|   | 4.2.4    | Buffer lifecycle and ownership         |    |

|   | 4.2.5    | Framebuffers                           |    |

|   | 4.2.6    | Processing elements                    |    |

|   | 4.2.7    | Resources                              |    |

|   | 4.2.8    | Providers                              |    |

|   |          | ntime reporting                        |    |

|   | 4.3.1    | Logs                                   |    |

|   | 4.3.2    |                                        | 23 |

|   | 4.3.3    | Tracing                                |    |

|   |          | ialization files                       |    |

|   | 4.4.1    | Syntax                                 |    |

| _ | 4.4.2    | Example                                |    |

| 5 | -        | e API                                  |    |

|   |          | eams                                   |    |

|   | 5.1.1    | Restrictions                           |    |

|   | 5.1.2    | Stream and scalar parameter attributes |    |

|   | 5.1.3    | Example                                | 31 |

|       | 5.2  | Strea        | ım functions                     | 32 |

|-------|------|--------------|----------------------------------|----|

|       | 5.2  | 2.1          | Count                            | 32 |

| 5.2.2 |      | 2.2 I        | Block loads and stores           | 33 |

|       | 5.2  | 2.3          | Strided loads and stores         | 33 |

|       | 5.2  | 2.4 I        | Indexed loads and stores         | 33 |

|       | 5.2  | 2.5          | Scalar output                    | 33 |

| 6     | Ke   | rnel A       | PI                               | 34 |

|       | 6.1  | Kern         | els                              | 34 |

|       | 6.1  | 1 I          | Limitations                      | 35 |

|       | 6.2  | DPU          | basic types                      | 36 |

|       | 6.2  | 2.1          | Type conversions                 | 36 |

|       | 6.2  | 2.2 I        | DPU booleans                     | 37 |

|       | 6.3  | Scala        | ar and vector variables          | 37 |

|       | 6.4  | Array        | ys                               | 37 |

|       | 6.5  | Oper         | ators                            | 38 |

|       | 6.6  | Cont         | rol flow constructs              | 39 |

|       | 6.7  | Strea        | ım access functions              | 40 |

|       | 6.7  | '.1 S        | Sequential streams               | 41 |

|       | 6.7  | '.2 <b>(</b> | Conditional streams              | 41 |

|       | 6.7  | '.3 <i>I</i> | Array streams                    | 42 |

|       | 6.8  | Intrin       | nsic operations                  | 42 |

|       | 6.8  | 3.1          | Saturation arithmetic            | 43 |

|       | 6.8  | 3.2 I        | Fractional arithmetic            | 43 |

|       | 6.8  |              | Multiplication intrinsics        |    |

|       | 6.9  | rep          | peat                             | 45 |

|       | 6.10 | #pr          | ragma pipeline                   | 45 |

|       | 6.11 | #pi          | ragma local_array_size           | 45 |

| 7     | De   | mo Ap        | oplication spm_demo              | 47 |

|       | 7.1  | Testb        | pench main                       | 47 |

|       | 7.2  | Data         | representation                   | 48 |

|       | 7.3  | Imple        | ementation alternatives          | 48 |

|       | 7.4  | Buffe        | er allocation                    | 49 |

|       | 7.5  | Strea        | ıms                              | 49 |

|       | 7.6  | Kern         | els                              | 51 |

|       | 7.7  | File i       | input component                  | 53 |

|       | 7.7  |              | Component definition             |    |

|       | 7.7  | ′.2 I        | Properties function              | 54 |

|       | 7.7  |              | Instance initialization function |    |

|       | 7.7  | '.4 <b>(</b> | Command handler function         | 56 |

|       | 7.7  | '.5 I        | Execute function                 | 57 |

|       | 7.7  | ′.6 I        | Destroy function                 | 58 |

|       |      |              |                                  |    |

|    | 7.8  | File output component                  | 58  |

|----|------|----------------------------------------|-----|

|    | 7.9  | Green screen removal component         | 59  |

|    | 7.10 | Component main                         | 60  |

|    | 7.1  | 10.1 Initialization file               | 62  |

| 8  | Co   | ommand line tools                      | 6   |

|    | 8.1  | Functional mode: Run on host           | 64  |

|    | 8.2  | Simulate with spsim                    | 65  |

|    | 8.3  | Run on hardware                        | 65  |

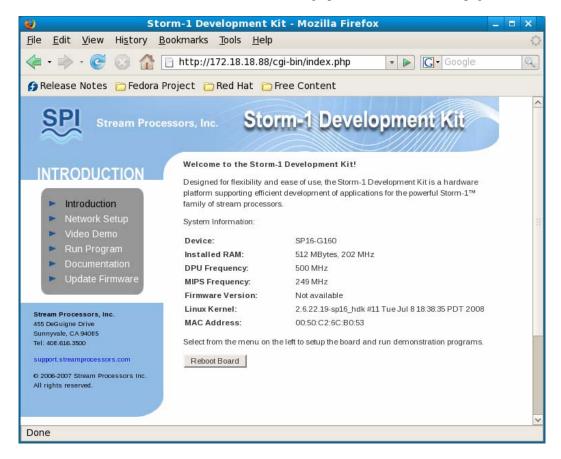

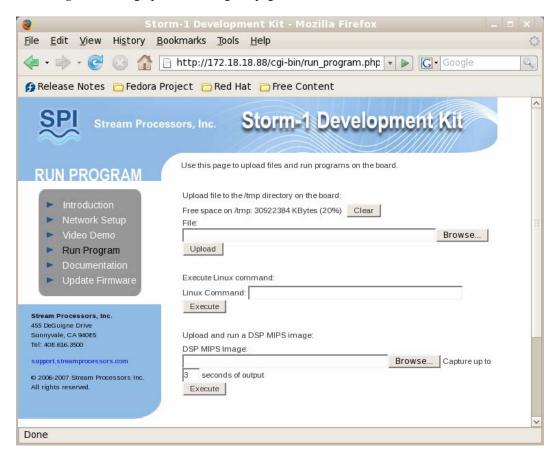

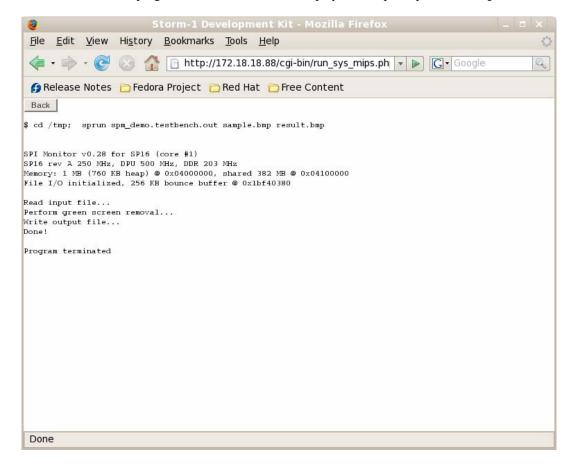

|    | 8.3  | Run from web page                      | 67  |

|    | 8.4  | Run application on host or on DSP MIPS | 70  |

|    | 8.5  | Run application on hardware            | 70  |

|    | 8.5  | 5.1 Initialization file                | 71  |

|    | 8.6  | Logs                                   | 71  |

|    | 8.7  | Timers                                 | 72  |

|    | 8.8  | Performance                            | 73  |

| 9  | Str  | ream Program Development               | 74  |

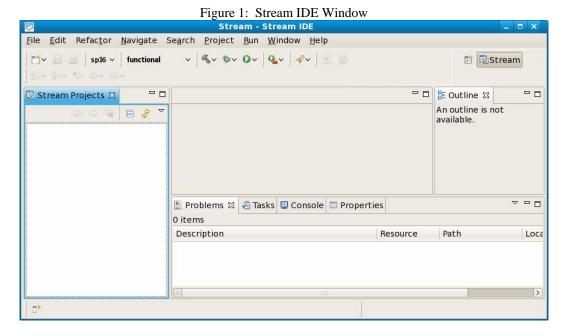

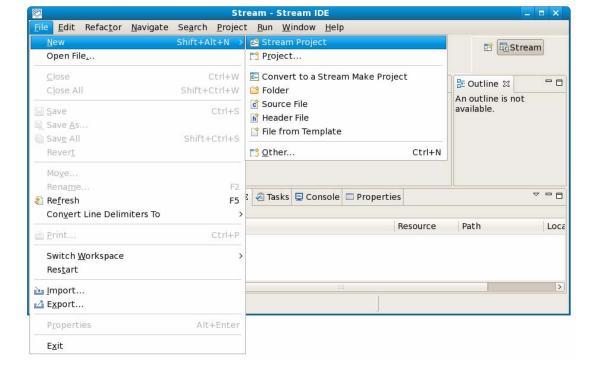

|    | 9.1  | Invoke spide                           | 75  |

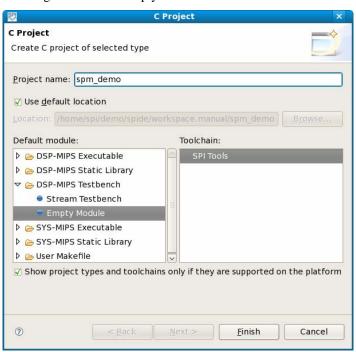

|    | 9.2  | Create a project                       | 77  |

|    | 9.2  | • •                                    |     |

|    | 9.2  | • •                                    |     |

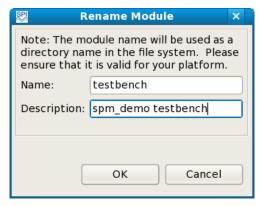

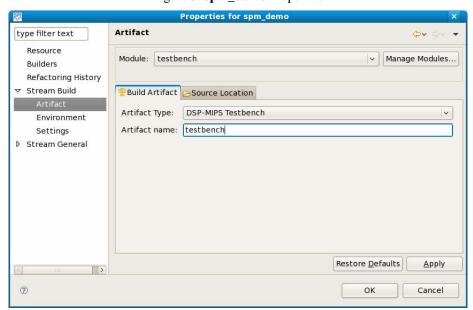

|    | 9.2  | 2.3 Create testbench module            | 81  |

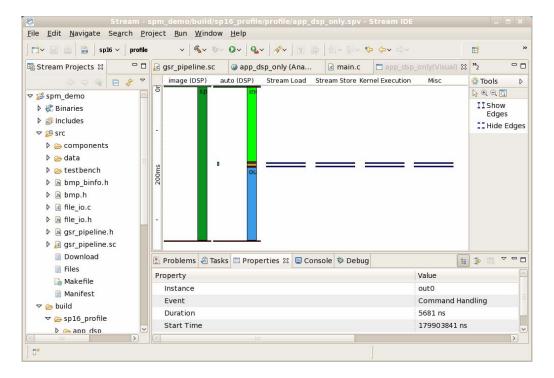

|    | 9.3  | Functional mode                        | 83  |

|    | 9.3  | 3.1 Build                              | 83  |

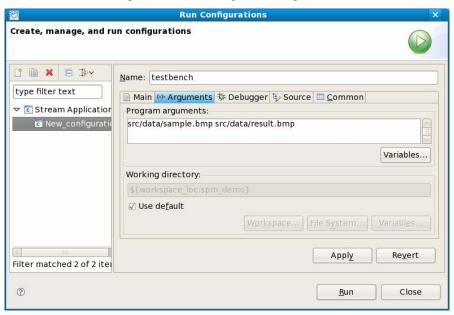

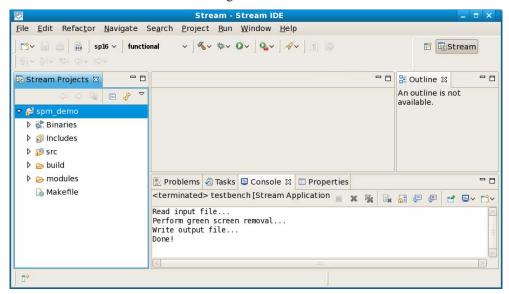

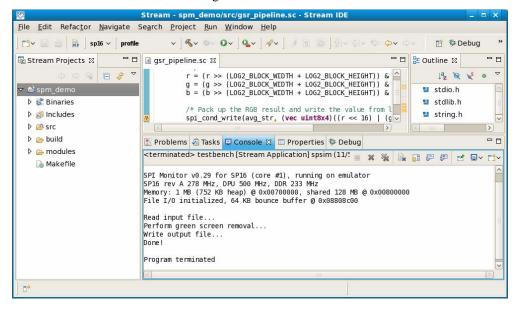

|    | 9.3  | Run on host                            | 84  |

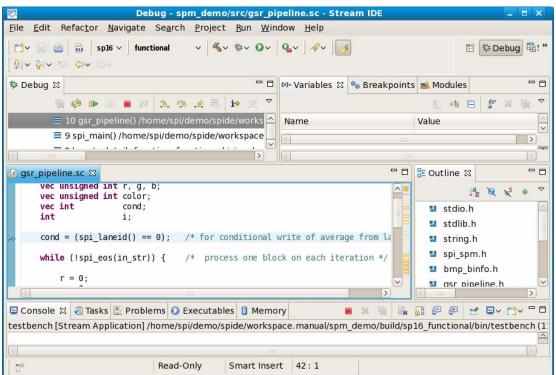

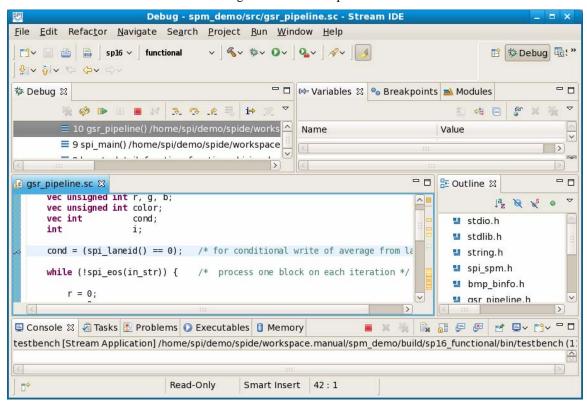

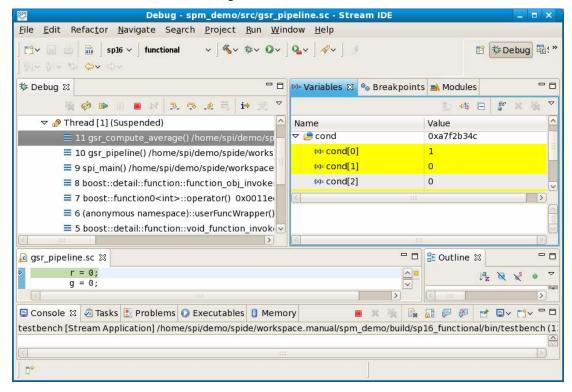

|    | 9.3  | 3.3 Debug                              | 86  |

|    | 9.3  | 3.4 Fast functional mode               | 88  |

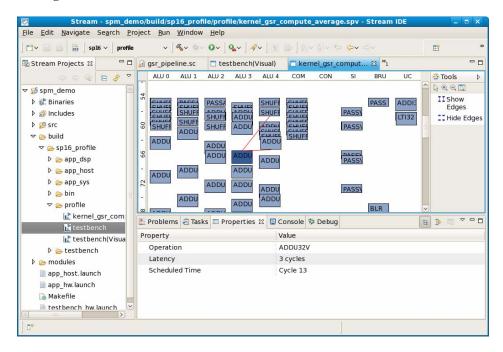

|    | 9.4  | Profile mode                           | 89  |

|    | 9.4  | 4.1 Build                              | 89  |

|    | 9.4  | 1.2 Run under simulator                | 89  |

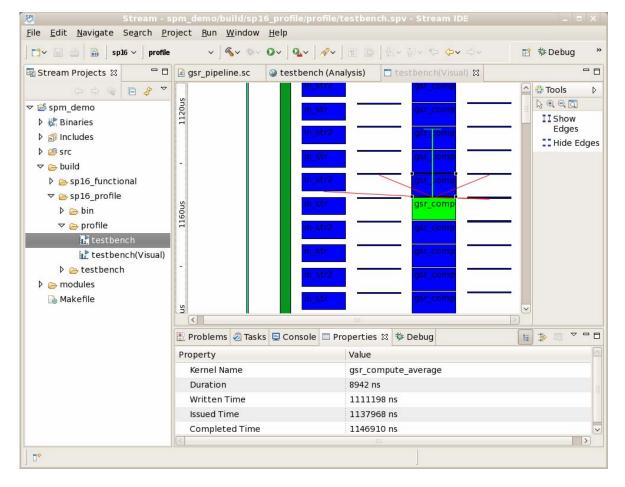

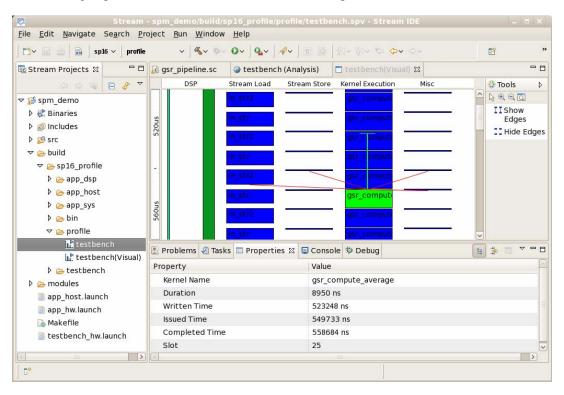

|    | 9.4  | View profile data                      | 90  |

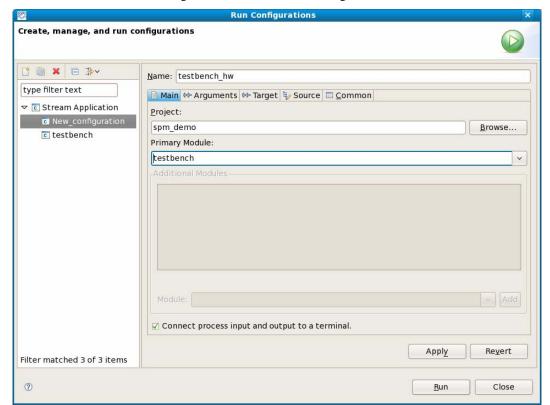

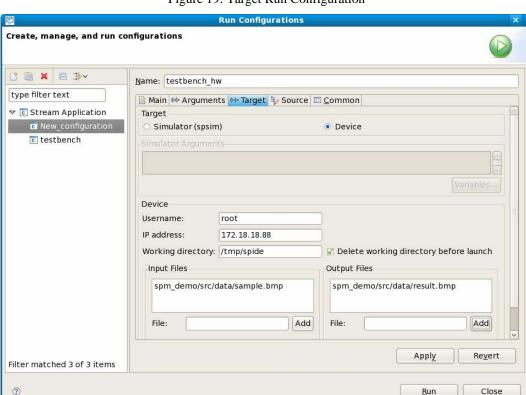

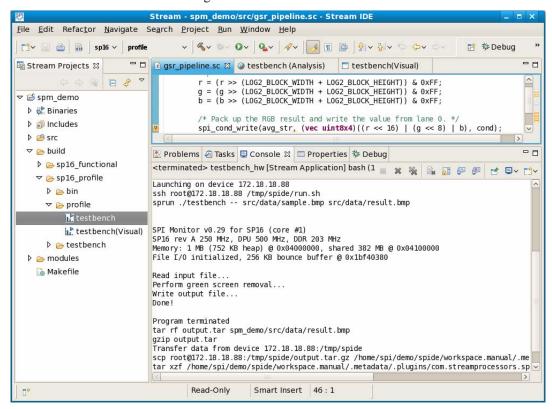

|    | 9.4  | 4.4 Run on hardware                    | 91  |

|    | 9.5  | Release mode                           | 94  |

|    | 9.6  | Complete application                   | 95  |

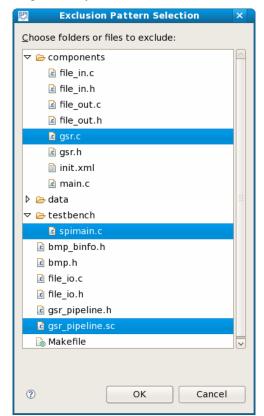

|    | 9.6  | •                                      |     |

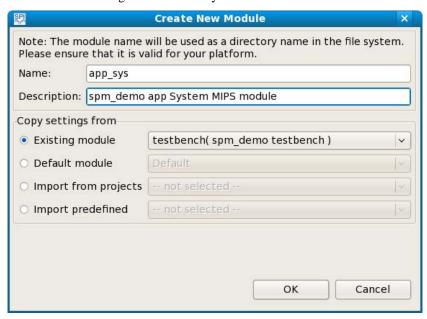

|    | 9.6  | 5.2 Create DSP MIPS Module             | 97  |

|    | 9.6  | Run application                        | 98  |

|    | 9.7  | Import a project                       | 100 |

|    | 9.8  | Use Makefile from command line         | 100 |

| 10 | Per  | rformance optimization                 |     |

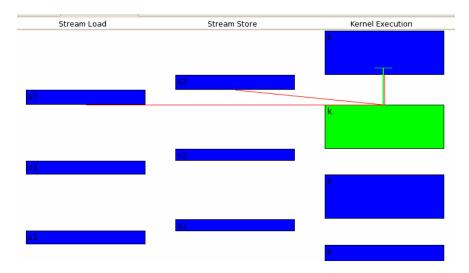

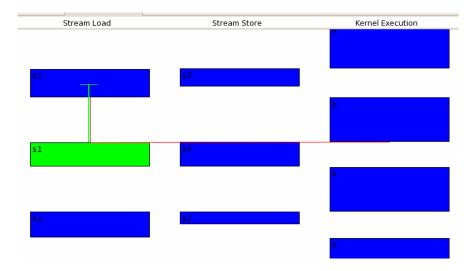

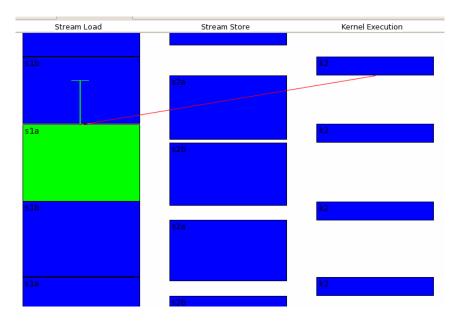

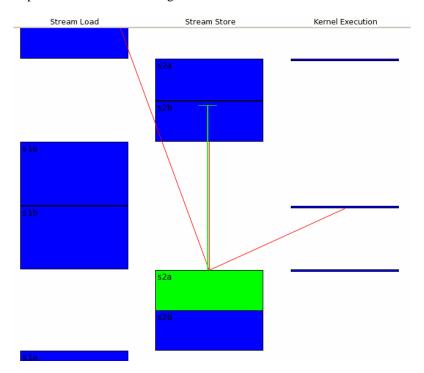

|    | 10.1 | Pipelines                              | 103 |

|    | 10.2 | Visualization                          | 105 |

| 12 | Index  |                                         | 125 |

|----|--------|-----------------------------------------|-----|

| 11 | Gloss  | ary                                     | 122 |

|    | 10.6.5 |                                         |     |

|    | 10.6.4 | Software pipeline                       | 120 |

|    | 10.6.3 | Remove control flow                     | 120 |

|    | 10.6.2 |                                         |     |

|    | 10.6.1 | 1 0210                                  |     |

| 1  | 0.6    | Kernels                                 |     |

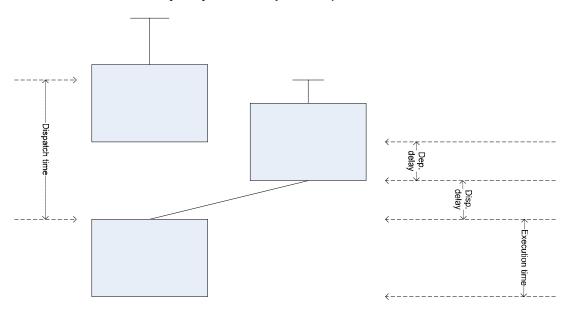

|    | 10.5.2 | Dispatch delays                         | 117 |

|    | 10.5.1 | - · r · · · · · · · · · · · · · · · · · |     |

| 1  | 0.5    | Stream operations                       | 112 |

| 1  | 0.4    | Tables                                  | 108 |

| 1  | 0.3    | Components                              | 107 |

|    |        |                                         |     |

## 1 Introduction

A *stream processor* is a high performance programmable processor for digital image processing and digital signal processing (DSP) applications. The stream processors of Stream Processors, Inc. (SPI) are programmable in an extended version of the C programming language, using the *Stream programming model* (SPM). The Stream programming model exposes the parallelism and locality inherent in an application program, and the SPI processor design and software development tools exploit this parallelism and locality in hardware.

This document gives a tutorial introduction to Stream programming and to the use of SPI Stream tools. It describes how to install the SPI Stream tools. It presents the essential concepts of SPI stream processors that you must understand to write efficient Stream programs. It describes the Stream extensions to the C language and the application programming interface (API) to the Stream programming model. It uses a demo program as a detailed introductory Stream programming example. It describes stream program development flow under an integrated development environment (IDE).

A companion volume, *Stream Reference Manual*, contains detailed reference information on Stream programming and on the tools in the Stream toolset. *Stream Release Notes* gives specific information related to the current release of the Stream tools.

# 1.1 Typographical conventions

This manual indicates a definition by setting the defined word in *italic* type. Italic type also indicates a placeholder that may take on different values; for example, an *n*-bit object might contain 8, 16, or 32 bits. **Bold** type indicates filenames and programming language literals; for example, **int** is a C data type. Monospace typeface Courier is used for command line input text and for C and Stream program fragments.

# 1.2 Document revision history

| <b>Document number</b> | Date          | Description     | Release Version |

|------------------------|---------------|-----------------|-----------------|

| SWUG-00001-001         | December 2007 | Initial release | RapiDev 1.0     |

| SWUG-00001-002         | January 2008  | Revision        | RapiDev 1.0.1   |

| SWUG-00001-003         | April 2008    | Revision        | RapiDev 1.0.2   |

| SWUG-00001-004         | June 2008     | Major revision  | Stream 2.0      |

| SWUG-00001-005         | August 2008   | Revision        | Stream 2.1      |

| SWUG-00001-006         | December 2008 | Revision        | Stream 2.2      |

| SWUG-00001-007         | March 2009    | Revision        | Stream 2.3      |

## 2 Installation

This chapter describes the installation of SPI Stream tools for Linux. Shell script **install.sh** installs the toolset from compressed **tar** archive files on the SPI customer support website or on a distribution CD.

The Stream development environment runs on a Linux host system and compiles Stream programs using a **gcc**-based MIPS cross compiler. The toolset is extensively tested running on FedoraCore 8.0, but it should also run successfully on most other x86 Linux distributions.

For users who wish to run the SPI Stream tools under Windows, SPI provides a Linux virtual machine that runs under the free VMware player (see <a href="www.vmware.com/products/player/">www.vmware.com/products/player/</a>). A separate document VMware Player Installation and Setup Guide provides instructions for the installation and use of the SPI VMware distribution.

### 2.1 Install the toolset

You should normally run as the superuser **root** to install the SPI Stream tools under Linux. If you need to install the tools on a machine on which you do not have root privileges, first install the SPI virtual machine distribution, and then perform the installation as **root** under the VMware player. Alternatively, you can specify the **-no\_root** option to the installation script **install.sh**; in this case, the installation will not include an NFS-mountable filesystem for use with Linux running on System MIPS on an SPI development board.

Shell script **install.sh** installs the Stream distribution from a source (for example, the SPI customer support website or a distribution CD) to an arbitrary destination. By default, it downloads packages required for installation. Its usage is:

```

Usage: install.sh [ option ... ]

Options:

-d dest

-no_root

Install to given directory dest [default: /opt/spi/Stream_nnn]

-no_root

-rep

Use directory rep as package download repository [default: /opt/spi/download]

-s src

-url url

Download and install packages from url [default: SPI website]

```

To install the Stream distribution from the SPI customer support website, type:

```

$ ./install.sh [ -d dest ]

```

where *dest* gives an optional destination (default: /opt/spi/Stream\_nnn). To install from a CD distribution instead, use the -s option:

```

$ src/install.sh -s src [ -d dest ]

```

where src gives the Stream distribution location (e.g., /media/Stream\_nnn for a mounted CD).

After the installation is complete, you must add the Stream tools **bin** and **lib** directories to the settings of environment variables **PATH** and **LD\_LIBRARY\_PATH**, respectively. For example, for the **bash** shell, type:

```

export LD_LIBRARY_PATH=dest/lib:$LD_LIBRARY_PATH

export PATH=dest/bin:$PATH

```

You may want to add these lines to your \$HOME/.bashrc or to the global /etc/bashrc.

The **bsp** directory in the Stream distribution contains firmware for an SPI development board. It may be used to update board firmware using the on-board web pages. The **bsp** directory also includes compressed **tar** files containing sources. These sources are supplied in compliance with the <u>GNU Public License</u>.

## 2.2 Distribution contents

This section gives a quick overview of the directory structure of the Stream distribution.

benchmark/ benchmark programs

**bin/** binaries

**bsp/** hardware board support package

**demos/** demo programs

demos/spm\_demo Stream programming model demo application

doc/ documentation include/ header files

installed\_pkgs/ installed package repository

internal/ toolset internals

lib/ libraries

linux/System MIPS Linux distributionlinux/target/System MIPS Linux root filesystem

Later chapters of this manual use **spm\_demo** to illustrate the Stream programming model and the use of the Stream tools. The **demos**/ directory includes a video demo application **video\_demo** in addition to **spm\_demo**.

The **doc**/ directory includes *Stream User's Guide*, *Stream Reference Manual*, and *Storm-1 Benchmarks* in PDF format.

# 3 Stream Programming

A stream processor contains a *general purpose unit* (GPU) for data handling and control, a *data parallel unit* (DPU) for compute-intensive inner loop computations, and *peripheral units* for device i/o. The Storm-1 processor GPU contains two MIPS processors: *System MIPS* (running Linux) handles user interface and device i/o, while *DSP MIPS* handles communication with the DPU.

A stream processor application program begins execution on System MIPS. The System MIPS application is a C source program (extension .c), compiled to a MIPS executable object that runs under Linux on System MIPS. The application may load and execute a DSP MIPS image, compiled by the Stream compiler **spc** from a Stream source program (extension .sc). The DSP MIPS image may in turn load and execute *kernel functions* on the stream processor DPU; the Stream source program defines both the DSP MIPS portion and the DPU portion of the program. The execution of System MIPS, DSP MIPS and DPU is asynchronous, with the Stream programming model handling any required synchronization.

A *stream* represents a sequence of structured data elements called *records*, each of the same type, stored in the lane register file (LRF) of a stream processor. A *kernel function* (or simply *kernel*) performs a computationally intensive operation on one or more input streams and produces one or more output streams. The DPU can access memory in the LRF, in a scalar operand register file (SORF), and in an operand register file (ORF), but it cannot access arbitrary memory. As a result, a Stream program running on DSP MIPS communicates with a kernel function running on the DPU only by means of streams (stored in the LRF) and scalar variables (stored in the SORF) that are the kernel function's arguments.

A kernel function is like a C function, but with some limitations on the types of statements that it can use; kernels are designed for high performance, which restricts the language features available in kernel code. A Stream program defines streams and passes streams as arguments to or from kernels, and stream processor hardware allows a kernel to access stream data efficiently. When kernel execution terminates, the Stream program can process the kernel's output streams and read the values returned from the kernel by scalar output variables.

The DPU design is a *VLIW* (very large instruction word) *SIMD* (single instruction, multiple data) architecture. The VLIW design allows the DPU to issue simultaneous instructions to multiple arithmetic-logical units (ALUs) in each hardware cycle. The SIMD design executes each instruction ("single instruction") simultaneously in multiple independent arithmetic processors called *lanes* (8 in SP8, 16 in SP16), with each lane operating on different data ("multiple data"). A kernel can perform multiple operations on multiple records in a data stream concurrently, resulting in very high efficiency.

# 3.1 Stream programming model

The SPI Stream programming model (SPM) is a parallel programming and execution model for stream processors. It allows the programmer to create Stream programs that use the powerful hardware features of a stream processor efficiently. It covers all levels of embedded system programming, from low-level data-parallel programming to efficient high-level multi-core parallelism. It consists of three application programming interfaces (APIs), each described in detail in a later chapter of this document:

- The Component API captures multi-core parallelism in a high-level modular program design framework.

- The *Pipeline API* uses on-chip memory management to communicate data efficiently between parts of a stream processor.

- The Kernel API captures data-level parallelism with direct access to efficient kernel operations.

The Stream programming model uses the C language with simple extensions to support data-parallel programming.

The Stream execution model is based on a set of connected components operating in a data-flow manner. An application calls **spi\_spm\_start** to start the Stream programming model runtime and calls **spi\_spm\_stop** to stop it. Alternatively, a program compiled with **spc** option **-m testbench** starts the SPM runtime automatically before it calls the user-supplied **spi\_main** function.

Later chapters introduce the essential concepts of each Stream programming model API. Chapter <u>Demo Application spm\_demo</u> uses a demo program to demonstrate the use of the APIs. *Stream Reference Manual* gives a detailed description of each SPM data type and function.

# 3.2 Stream language extensions

This section describes the language used for Stream programs, which is just standard C with a few extensions. A program can define structured record types and streams. It can define kernels that take streams and scalar variables as arguments. It can invoke kernels and execute special functions to control kernels and streams.

Many features of the Stream language are taken directly from standard C and are therefore not described here; see e.g. the C Standard (*American National Standard for Programming Languages – C*, ANSI/ISO 9899-1990, ISO/IEC 14882) for details. Lexical elements of the language are the same as C, except that several new keywords are added, as detailed in the <u>Added keywords</u> section below. Stream code outside of kernel functions is compliant with the C Standard, but kernel code supports a restricted subset of C, as described in the <u>Kernel API</u> chapter. The DSP MIPS runtime does not fully support the standard C library; see the *DSP MIPS Standard Library Functions* chapter of the *Stream Reference Manual* for details.

The Stream compiler **spc** compiles Stream programs. **spc** requires definitions from header file **spi\_spm.h**, so all Stream programs must #include "spi\_spm.h".

## 3.2.1 Added keywords

The Added keywords section of the Stream Reference Manual gives a complete list of the keywords reserved for use by a Stream program in addition to the usual C keywords. Type modifiers **kernel** and **stream** identify kernels and streams. Type modifier **vec** in kernel code identifies a vector variable (i.e., a variable with a different value in each lane of the DPU). Types **int32x1**, **int16x2**, **int8x4**, **uint32x1**, **uint16x2**, and **uint8x4** represent DPU data types (one

32-bit signed integer, two 16-bit signed integers packed into one 32-bit word, and four 8-bit signed integers packed into one 32-bit word, plus their unsigned counterparts). The **\_\_repeat**\_\_ keyword repeats a program block.

#### 3.2.2 Predefined macros

The *Predefined macros* section of the *Stream Reference Manual* gives a complete list of preprocessor macros defined during compilation by the Stream compiler **spc**. Most of the macros depend on compilation options. Macro **SPI\_LANES** defines the number of lanes in the DPU (16 on SP16, 8 on SP8).

# **3.2.3 Types**

This section describes Stream types. In addition to the usual C data types, Stream programs can use DPU basic types (described in the <a href="DPU basic types">DPU basic types</a> section below), user-defined structured record types, and stream types.

#### 3.2.3.1 Standard C types

Stream programs can use standard C data types:

- char and unsigned char are represented by an 8-bit byte.

- **short** and **unsigned short** are represented by a 16-bit halfword (two bytes).

- int, unsigned int, long and unsigned long are represented by a 32-bit word (four bytes).

- Pointers are represented by a 32-bit word (four bytes).

- **float** is represented by a 32-bit word (four bytes).

- **double** and **long double** are represented by a 64-bit dword (eight bytes).

- C9X types **long long** and **unsigned long long** are represented by a 64-bit dword (eight bytes).

Signed integers use 2's complement representation. Floating point types use IEEE format. Stream stores multibyte data in littleendian format. If **unsigned integer i** contains 0x03020100, Stream stores its bytes to successive increasing memory locations as 0x00, 0x01, 0x02, 0x03. Similarly, if **unsigned short s** contains 0x0100, Stream stores its bytes to successive increasing memory locations as 0x00, 0x01.

Kernels defined in Stream programs can use only special DPU basic types; see the <u>DPU basic types</u> section below for details.

#### 3.2.3.2 Structured types

Stream functions and kernel functions use user-defined structured data types to represent stream data conveniently and concisely. A structure represents a fixed-length data *record* that forms a single element of a stream. It contains one or more members, where each member is a DPU basic type or a previously defined structured record type. For example,

```

typedef struct {

int32x1 x, y, z;

} xyz;

```

defines type **xyz** that consists of three **int32x1** (32-bit signed integer) values. The structure name can be used as a new type. As in standard C usage, the member operator "." provides access to a member of a record.

Stream does not permit bit-field structure members. Stream currently does not permit nested structures; only single-level **struct** is allowed. Structure members currently must be basic Stream types, not user-defined types.

# 4 Component API

This section introduces the basic elements of the Component API: components, buffers, ports, connections, commands and responses, instance states, execution requirements, the Stream execution model, logging, tracing, and timers.

#### 4.1 Basics

## 4.1.1 Components

The *component* is the central concept of the Stream programming model. A component is a high-level data-driven computational module that typically reads input data from one or more input ports and writes output data to one or more output ports (though a source component only has output ports and a sink component only has input ports). A program may define components and may use components from supplied component libraries. The abstract modular nature of component definition encourages the interoperability and reuse of component libraries.

An application can create multiple *instances* of a component. For example, an application might invoke two instances of the same multiplexing component to produce two streams of output data from four streams of input data.

Within a component, program execution follows the familiar C programming model of single-threaded sequential execution. The Stream programming model frees the programmer from the burden of dealing with deadlock, race conditions, mutual exclusion, and data coherence (cache) issues.

Data type **spi\_component\_t** represents a component and **spi\_instance\_t** represents a component instance. An instance-specific context of type **spi\_instance\_context\_t** identifies each instance. The Stream programming model defines the component functions listed below; see *Stream Reference Manual* for details.

spi\_component\_find

Find a component with a given name and provider

spi\_component\_get\_desc

spi component get name

Get the description of a component

Get the name of a component

• **spi\_component\_get\_provider** Get the provider (e.g., SPI) of a component

• spi component get version Get the version of a component

• SPI COMPONENT NEW Define a component

• **spi\_component\_set\_flags** Set the flags for a component

• spi\_component\_set\_resource\_requirements

Set the resource requirements for a component

• **spi\_get\_component** Get the name of the component for the current component instance

• **spi get name** Get the name of the current component instance

• **spi\_instance\_new** Create a new component instance

• spi\_schedgroup\_component\_find Find a component in a scheduling group

Macro **SPI\_COMPONENT\_NEW** defines a component. It takes as arguments five functions that specify the behavior of a component:

- the properties function defines properties of the component,

- the *instance initialization function* initializes a component instance,

- the destroy function destroys a component instance,

- the execute function executes a component instance when given conditions are satisfied, and

• the *command handler function* handles commands to a component instance.

A component properties function executes once, when the Stream programming model runtime begins execution; it can set component properties and resource requirements and register commands, ports, and execution requirements that apply to all instances of the component.. A component instance initialization function executes when **spi\_instance\_new** creates a new component instance. A component execution function executes when the component is running and specified execution properties are met; for example, a component might begin execution when input data is available on its input port and space is available on its output port. A component command handler handles component-specific commands.

The <u>Component definition</u> section of the <u>Demo Application spm\_demo</u> chapter below gives an example of the use of **SPI\_COMPONENT\_NEW**.

#### 4.1.2 Buffers

A *buffer* is a region of shared memory with a fixed size and alignment used to communicate data efficiently (i.e., without copying) between component instances. A Stream program must use a connection to pass a buffer between component instances; any other method results in undefined behavior. The use of buffers allows the programmer to write Stream code without explicit cache or processor synchronization code; the Stream programming model handles caching and synchronization issues automatically.

A Stream program uses a buffer as a data source for a Pipeline API **spi\_load\_\*** function or as a data destination for a **spi\_store\_\*** function . A kernel uses a Kernel API function **spi\_\*read** to read from a buffer and **spi\_\*write** to write to a buffer.

**spi\_buffer\_new** creates a new buffer with a given size, alignment, and flags. **spi\_buffer\_open** returns a pointer to the contents of a buffer (i.e., to the shared memory that the buffer represents). Buffer flags specify whether the buffer contents are readonly or reside in cached memory. **spi\_buffer\_close** closes a buffer and **spi\_buffer\_free** returns a buffer to a buffer pool.

spi\_connection\_pop pops a buffer from an input port and spi\_connection\_push pushes a buffer to an output port.

Data type **spi\_buffer\_t** represents a buffer. The Stream programming model defines the buffer functions listed below; see *Stream Reference Manual* for details.

spi\_buffer\_clone

spi\_buffer\_close

spi buffer free

Clone a buffer

Close a buffer

Free a buffer

• **spi\_buffer\_get\_info** Get buffer information

• spi\_buffer\_get\_info\_size Get the buffer information size

spi\_buffer\_get\_size

spi\_buffer\_merge

spi\_buffer\_new

Get buffer size

Merge cloned buffers

Create a new buffer

• **spi buffer open** Open a buffer (to allow access to its contents)

• **spi\_buffer\_set\_info** Set buffer information

spi\_connection\_pop

spi\_connection\_push

Pop a buffer from a connection

Push a buffer to a connection

spi\_get\_buffer\_heap\_highwater

Get the shared memory heap highwater mark

• spi\_get\_buffer\_heap\_size

Get the current shared memory heap size

spi\_load\_\*

spi\_pool\_get\_buffer

spi\_store\_\*

Load data from a buffer to LRF

Get a buffer from a buffer pool

Store data from LRF to a buffer

#### 4.1.2.1 Buffer pools

A *buffer pool* is a set of identically sized and aligned buffers. To avoid memory fragmentation, the Stream program model reuses buffers in a pool as they become available. Components and stream applications on System MIPS or on DSP MIPS can use buffer pools.

**spi\_pool\_new** creates a buffer pool with buffers of a given size and alignment. If the requested initial buffer count is non-zero, **spi\_pool\_new** allocates memory for the requested number of buffers.

spi\_pool\_get\_buffer gets a buffer from a buffer pool. If the pool does not have any available buffers but was created with the SPI\_POOL\_FLAG\_GROW flag, spi\_pool\_get\_buffer allocates memory for a new buffer. A Stream program can allocate and free memory with the standard C library memory allocation functions malloc, realloc, calloc, and free, but memory allocated with these functions cannot be used as a buffer and cannot be shared between instances.

The Stream programming model defines the buffer pool functions listed below; see *Stream Reference Manual* for details.

• **spi\_get\_pool** Get the pool with a given name

• **spi\_pool\_free** Free a buffer pool

• spi\_pool\_get\_avail\_buffer\_count

Get the number of buffers available from a pool

spi\_pool\_get\_buffer

spi\_pool\_get\_desc

spi\_pool\_get\_name

Get a buffer from a buffer pool

Get the description of a buffer pool

Get the name of a buffer pool

• spi\_pool\_new Create a buffer pool

#### 4.1.2.2 Buffer information

An application can optionally attach additional *buffer information* to a buffer. Buffer information typically specifies properties of the buffer data (for example, how much of the buffer data is valid).

**spi\_buffer\_set\_info** sets the information associated with a buffer, attaching a copy of the buffer information to the buffer. Thus, changing the contents of the specified object after this call does not change the information associated with the passed buffer.

**spi\_buffer\_get\_info** returns a pointer to the information associated with a buffer. Buffer information becomes invalid when ownership of the buffer is released. Before ownership of the buffer is released, the information associated with the buffer can be modified using the pointer returned by **spi\_buffer\_get\_info**.

### **4.1.3 Ports**

A *port* provides the data interface between a component and the outside world. A port is either an input port or an output port. A program creates a connection to a port to move data to it or from it. A component may allow multiple connections to a single port.

Data type **spi\_portdir\_t** defines the direction of a port (input or output). The Stream programming model defines the port functions listed below; see *Stream Reference Manual* for details.

spi\_port\_export

spi\_port\_get\_connection

spi\_port\_get\_connection\_count

Export a port on a contained instance

Get a connection attached to a port

Get the number of connections of a port

spi\_port\_get\_desc

spi\_port\_get\_dir

Get the description of a port

Get the direction of a port

• spi\_port\_get\_max\_connection\_count Get the maximum number of connections allowed on a port

**spi\_port\_get\_name** Get the name of a port

**spi\_port\_register** Define a port

#### 4.1.4 Connections

A Stream programming model application uses a *connection* to move data between component instances. A connection represents a single-writer single-reader FIFO that can contain a fixed number of buffers (the *depth* of the connection). **spi\_connect** creates a connection between ports of two existing component instances, while **spi\_connection\_new** creates a connection from an application to a port on a contained component instance. **spi\_connection\_push** and **spi\_connection\_pop** push/pop a buffer to/from a connection.

Data type **spi\_connection\_t** represents a connection. The Stream programming model defines the connection functions listed below; see *Stream Reference Manual* for details.

spi\_connect

spi\_connection\_get\_depth

spi\_connection\_get\_name

spi\_connection\_is\_empty

spi\_connection is full

Create a connection between instances

Get the FIFO depth of a connection

Determine if a connection is empty

Determine if a connection is full

• **spi\_connection\_new** Create a connection to a contained instance

spi\_connection\_pop

spi\_connection\_push

spi\_port\_get\_connection

Pop a buffer from a connection

Push a buffer to a connection

Get a connection on a port

# 4.1.5 Commands and responses

A Stream application or a component instance can send a *command* to a component instance, and the instance that receives the command can send back a *response* to indicate the success or failure of the command. Components and Stream applications on System MIPS or on DSP MIPS can send commands and responses.

A component defines the set of commands that it recognizes; the component's properties function calls **spi\_cmd\_register** to register each recognized command. For each command, the **spi\_cmd\_register** call also defines the format of the command *payload* (if any) and the format of the command *response payload* (if any). The **SPI\_COMPONENT\_NEW** macro that defines a component specifies a *command handler* function, invoked when an instance of the component receives a command. An instance may also call **spi\_response\_set\_handler** to register response handler functions. The SPM runtime calls a response handler function when an instance receives a response to a previously sent command.

#### Stream User's Guide

**spi\_instance\_new** creates a component instance, returning an instance handle. As there is no other way to obtain an instance handle, **spi\_cmd\_send** can only send commands to instances in the hierarchy of instances created under an instance, not to arbitrary instances.

When **spi\_cmd\_send** sends a command to a component instance, the receiving instance returns a **spi\_response\_t** response handle. Eventually, when the command handler of the receiving instance (specified by the **spi\_component\_instance\_cmdhandler\_fn\_t** function in the **SPI\_COMPONENT\_NEW** definition of the receiving component) finishes processing the command, it calls **spi\_cmd\_send\_response** to send the command response. The reponse handler of the sending instance (specified by **spi\_response\_set\_handler**) handles the response, using the **spi\_response\_t** handle returned by **spi\_cmd\_send** to identify the command. The command response may include data in the form of a response payload.

Data type **spi\_cmd\_t** represents a command. The Stream programming model defines the command functions listed below; see *Stream Reference Manual* for details.

• **spi\_cmd\_free** Free a command

• spi\_cmd\_get\_desc Get the command description

spi\_cmd\_get\_id

spi\_cmd\_get\_name

spi\_cmd\_get\_payload

Get the command id

Get the command name

Get the command payload

spi\_cmd\_get\_payload\_size

spi\_cmd\_get\_payload\_type

Get the size of the command payload

Get the type of the command payload

spi\_cmd\_get\_response\_payload\_type

Get the type of the command response payload

spi\_cmd\_registerspi\_cmd\_sendDefine a commandSend a command

• **spi\_cmd\_send\_response** Send a command response

Data type **spi\_response\_t** represents a response; **spi\_send\_command** returns a response. The Stream programming model defines the response functions listed below; see *Stream Reference Manual* for details.

• **spi\_response\_free** Free a response

spi\_response\_get\_errno

spi\_response\_get\_payload

Get the response error code

Get the response payload

spi\_response\_get\_payload\_size

spi\_response\_get\_payload\_type

Get the size of the response payload

Get the type of the response payload

• **spi\_response\_set\_handler** Set a response handler

• **spi\_response\_strerror** Get a string describing a response error code

#### 4.1.5.1 Command/response lifecycle

spi\_cmd\_send sends a command with a given ID to a component instance. The Stream runtime creates a spi\_cmd\_t command handle that represents the command and passes it to the receiving instance's command handler. The receiving instance then owns the spi\_cmd\_t object (including the optional command payload), which it should free with spi\_cmd\_free when it is no longer needed.

If the command handler does not recognize a command, it should free the **spi\_cmd\_t** handle and return 1; the Stream runtime then sends a response indicating that the command was not recognized. If the command handler recognizes the command, the receiving instance eventually should call **spi\_cmd\_send\_response** to send a command response; it can send the response immediately or at some future time. When the response has been sent and the **spi\_cmd\_t** object is no longer needed, the receiving instance should free it with **spi\_cmd\_free**.

The behavior of **spi\_cmd\_send** differs depending on whether it is called from a Stream application or from a component instance. A **spi\_cmd\_send** call from a Stream application returns only when the receiving instance returns a response; that is, the **spi\_cmd\_send** blocks while awaiting a response. The application should free the **spi\_response\_t** object returned by **spi\_cmd\_send** with **spi\_response\_free** when it is no longer needed.

In contrast, a **spi\_cmd\_send** call from a component instance always returns a **spi\_response\_t** response token immediately, before the receiving instance returns the actual response. If the sending instance does not need to be notified of the actual response, it should free the returned **spi\_response\_t** with **spi\_response\_free**. If the sending instance does need to be notified of the actual response, it should call **spi\_response\_set\_handler** to register a response handler. The sending instance will execute the registered response handler when it receives the actual response from the receiving instance. The sending instance should free the **spi\_response\_t** response once it is no longer needed.

## 4.2 Execution

## 4.2.1 Component instance states

An instance is always in one of three states: stopped (SPI\_INSTANCE\_STATE\_STOPPED), paused (SPI\_INSTANCE\_STATE\_PAUSED), or running (SPI\_INSTANCE\_STATE\_RUNNING). The Stream execution model places a newly created instance in the paused state, so the instance's execute function will never be called, even if its execution requirements are satisfied. An instance may change its own state with spi\_set\_state or may have its state changed by receiving a SPI\_CMD\_START, SPI\_CMD\_PAUSE, or SPI\_CMD\_STOP built-in command. For example, to have new instances of a component start in the running state, add the following command to the component's initialization function:

```

spi_set_state(SPI_INSTANCE_STATE_RUNNING);

```

Typically, the application or component that creates an instance controls the state of the created instance. The following command changes instance **i0** to the running state:

```

spi_response_t response;

response = spi_cmd_send(i0, SPI_CMD_START, NULL, 0);

```

Data type **spi\_instance\_state\_t** represents a component instance state. The Stream programming model defines the instance state functions listed below; see *Stream Reference Manual* for details.

spi\_get\_state

spi\_set\_state

Get the state of an instance

Set the state of an instance

### 4.2.2 Execution requirements

An *execution requirement* is a condition that must be satisfied before the Stream scheduler invokes the execute function of a component instance. The Stream programming model provides several types of execution requirements that can be combined to create complex conditions. Execution requirement functions may be invoked only within a component, either on System MIPS or on DSP MIPS; that is, a program may not invoke an execution requirement function directly.

Data type **spi\_execution\_requirement\_t** represents an execution requirement type. The Stream programming model defines the execution requirement functions listed below; see *Stream Reference Manual* for details.

• **spi\_exec\_req\_activate** Make an execution requirement active

• **spi\_exec\_req\_delete** Delete an execution requirement

• spi\_exec\_req\_is\_satisfied True if an execution requirement is satisfied

• spi\_exec\_req\_register Register an execution requirement

### 4.2.2.1 Execution requirement types

Stream supports the following execution requirement types:

• **SPI\_EXEC\_ALLOF** Satisfied if all of a set of execution requirements are satisfied; used to compose a set of execution requirements into a more complex execution requirement.

• SPI\_EXEC\_ALWAYS Always satisfied.

• **SPI\_EXEC\_ANYOF** Satisfied if any of a set of execution requirements is satisfied; used to compose a set of other execution requirements into a more complex execution requirement.

• SPI\_EXEC\_FD\_READ Satisfied if all of a set of file descriptors are ready for reading.

• SPI\_EXEC\_FD\_WRITE Satisfied if all of a set of file descriptors are ready for writing.

• SPI\_EXEC\_NEVER Never satisfied.

• SPI\_EXEC\_POOL Satisfied if all of a set of buffer pools are ready. A buffer pool is ready if it

contains at least one free buffer (that is, if the next call to  ${\bf spi\_pool\_get\_buffer}$

will return a buffer).

SPI\_EXEC\_PORT\_ALLOF Satisfied if all connections on a set of ports are ready. An incoming

connection is ready if its FIFO is not empty and an outgoing connection is ready

if its FIFO is not full.

• SPI\_EXEC\_PORT\_ANYOF Satisfied if any connection on a set of ports is ready. An incoming connection is ready if its FIFO is not empty and an outgoing connection is ready if its FIFO is not full.

#### 4.2.2.2 Execution requirement lifecycle

**spi\_exec\_req\_register** creates an execution requirement of a given type with a given id. If the properties function of a component creates execution requirements, the requirements apply to all instances of the component. The initialization, execute, or command handler functions of a component may also call **spi\_exec\_req\_register** to add additional execution requirements for a component instance.

By default, all execution requirements for a component instance must be satisfied before the instance's execute function is invoked. If an instance has no registered execution requirements, its execute function is always ready to be invoked. As an alternative to the default behavior, **spi\_exec\_req\_activate** specifies a single execution requirement for an instance. **spi\_exec\_req\_activate** may be called as often as desired to change the active execution requirement.

**spi\_exec\_req\_delete** removes an execution requirement for an instance. If all execution requirements of an instance are removed, the instance's execute function is assumed to always be ready to be invoked.

#### 4.2.3 Scheduling priorities

Each instance has a scheduling priority, with priority level 0 being the highest priority and priority level 15 the lowest. By default, all new instances are initially at priority level 8. **spi\_set\_priority** can change the priority of an instance. Sending built-in command **SPI\_CMD\_SET\_PRIORITY** to an instance also can change its priority level.

#### Stream User's Guide

The scheduling priority is an integer. The Stream programming model defines the scheduling priority functions listed below; see *Stream Reference Manual* for details.

spi\_get\_priority

spi\_set\_priority

Get the scheduling priority of an instance

Set the scheduling priority of an instance

#### 4.2.3.1 Scheduling groups

Component instances within a group of instances called a *scheduling group* compete to have their execute functions invoked. A single image may contain any number of scheduling groups. By default, all components in an image are in the same default scheduling group. If a component is explicitly assigned to one or more scheduling groups in an image with **spi schedgroup register component**, it is not placed in the default scheduling group of the image.

A typical Storm-1 application consists of two images: a System MIPS image that contains a **main** function plus zero or more components that execute on System MIPS, and a DSP MIPS image that contains one or more components that execute on DSP MIPS (including all components that use the DPU). Thus, a typical application has two scheduling groups: one runs on System MIPS and one runs on DSP MIPS. Macro **SPI\_SCHEDGROUP\_NEW** creates a new scheduling group explicitly.

Each scheduling group controls all component instances created from components in the group. All component instances in a scheduling group compete for scheduling based on their priority, state, and execution requirements. Once an instance's initialization, execute, command handler, or response handler function is invoked, that function is guaranteed to complete before the scheduler invokes any other function of an instance from the scheduling group; the instance's functions are never preempted.

Each scheduling group maintains 16 priority queues, one for each scheduling priority level. Within a priority queue, ready instances are scheduled in round-robin order. The scheduler searches the queues in priority order to find a ready instance: if queue 0 (the highest priority) contains no ready instance, the scheduler searches for a ready instance in queue 1, and so on.

Each scheduling group uses the following processing loop:

- Command and response processing:

- o Check each instance for incoming commands.

- If any, invoke the instance's command handler function for the incoming command.

- Check each instance for incoming responses.

- If any, invoke the response handler associated with the response.

- Schedule execution:

- o Search the priority queues for the highest-priority ready instance

- Invoke the execute function for the instance.

- After execution, move the instance to the end of its priority queue.

The Stream programming model defines the scheduling group functions listed below; see *Stream Reference Manual* for details.

• **spi\_schedgroup\_component\_find** Find a component in a scheduling group

• SPI\_SCHEDGROUP\_NEW Define a new scheduling group

• **spi\_schedgroup\_register\_component** Register a scheduling group component

spi\_schedgroup\_set\_controlled\_resources

spi\_schedgroup\_set\_min\_stacksize

Set the minimum stacksize for a scheduling group

• spi schedgroup set processing elements Set the processing elements required for a scheduling group

## 4.2.4 Buffer lifecycle and ownership

### 4.2.4.1 Buffer lifecycle

The component instance or Stream application that creates a buffer pool with **spi\_pool\_new** owns the pool. Only the owning instance or application can call functions that use the pool; a pool cannot be shared or communicated to other instances or applications. A component properties function cannot create a pool; instead, its instance initialization function can create a pool, so that each instance of the component gets its own pool. The command handler function or the execute function of a component instance also can create a buffer pool.

**spi\_buffer\_clone** creates a new buffer that represents the same memory region as an existing buffer. Cloning a buffer allows multiple component instances to access the same buffer data. Because different instances can execute in arbitrary order or even concurrently, the use of buffer clones potentially can lead to non-deterministic behavior if a buffer clone writes to a memory location accessed by another buffer clone. To avoid this non-determinism, buffer clones should only access non-overlapping memory locations (though multiple clones can read from the same location without introducing non-deterministic behavior). Future Stream implementations will provide debugging support to verify that buffer clones do not access overlapping memory.

If a Stream application writes to two or more buffers that represent the same memory region, it must use **spi\_buffer\_merge** to unify the buffers into a new buffer that consolidates the writes. **spi\_buffer\_merge** can only merge buffers that represent the same memory region.

When a buffer is no longer needed, a Stream application or component may free it with **spi\_buffer\_free** or **spi\_buffer\_merge**. When all buffers that represent a memory region have been freed, the memory region returns to the buffer pool and becomes available for reuse.

**spi\_load\_\*** loads a stream with the contents of a buffer so that the DPU can read the buffer's data from a stream. Similarly, **spi\_store\_\*** stores a stream to a buffer so that DSP MIPS can access the buffer's data. A program can use these pipeline API functions to modify buffer data. If the program instead wishes to access buffer data directly (e.g., through a pointer to the buffer data), it must first call **spi\_buffer\_open** to obtain a pointer to the memory region the buffer represents. The program then can read or write data within the region through the pointer. When the program is finished with its direct access to the buffer data, it should call **spi\_buffer\_close** to invalidate the pointer returned by **spi\_buffer\_open**, disallowing further accesses to the buffer's memory region using that pointer. A buffer cannot be opened if it is already open.

If a program only needs to read the contents of a buffer, it should call **spi\_buffer\_open** with flag **SPI\_BUFFER\_FLAG\_READONLY**. By default, a buffer is in uncached memory, but flag **SPI\_BUFFER\_FLAG\_CACHED** can be used to obtain a buffer in cached memory instead. **spi\_buffer\_close** flushes cached buffers to propagate all buffer modifications to memory.

#### 4.2.4.2 Buffer ownership

A buffer has at most one owner at any time, and buffer ownership changes as a buffer is transferred between component instances and Stream applications. An instance may open, close, or free a buffer, or use the buffer as an argument to a **spi\_load\_\*** or **spi\_store\_\*** function, only if the instance owns the buffer.

Initially, the instance or application that gets a buffer with **spi\_buffer\_new** or **spi\_pool\_get\_buffer** owns the buffer. The owning instance or application releases buffer ownership when it frees the buffer with **spi\_buffer\_free**, when it

merges the buffer with **spi\_buffer\_merge**, or when it pushes the buffer onto a connection with **spi\_connection\_push**. An instance or application takes ownership of a new buffer created with **spi\_buffer\_clone** or **spi\_buffer\_merge**, and also takes ownership of a buffer popped from a connection with **spi\_connection\_pop**.

#### 4.2.5 Framebuffers

A *framebuffer* is part of a Linux graphical abstraction layer, as described in the Wikipedia article <u>Linux framebuffer</u> and in Linux documentation. A System MIPS application can initialize framebuffer use, for example with command **fbset** or through /dev/fb\*. The following Stream programming model functions provide framebuffer support:

• **spi\_fb\_get\_line\_length** Get the line length of a framebuffer in bytes

• spi\_fb\_get\_pixel\_type Get the pixel type of a framebuffer

spi\_fb\_get\_xres

spi\_fb\_get\_yres

Get the horizontal (X) resolution of a framebuffer in pixels

Get the vertical (Y) resolution of a framebuffer in pixels

spi\_fb\_is\_fb\_available

spi fb pool new

Check whether a framebuffer is available

Create a new framebuffer buffer pool

# 4.2.6 Processing elements

A Stream programming model *processing element* represents a hardware processor (for example, System MIPS or DSP MIPS) on which a scheduling group can execute. Some components might be coded to run on either System MIPS or DSP MIPS. Other components might be tied to a specific processor: a device i/o component might require System MIPS resources, while a component that uses the DPU must run on DSP MIPS to communicate with the DPU.

Data type **spi\_pels\_t** represents a set of processing elements. Function **spi\_load\_image** loads a program image on a processing element.

#### 4.2.7 Resources

A Stream programming model *resource* represents a hardware or software resource (for example, the DPU).

Data type **spi\_resources\_t** represents a set of resources. The Stream programming model defines the timer functions listed below; see *Stream Reference Manual* for details.

spi\_component\_set\_resource\_requirements

spi\_schedgroup\_set\_controlled\_resources

Set the resource requirements for a component

Set the resource resources for a scheduling group

#### 4.2.8 Providers

A *provider* is an organization that provides Stream programming model components. For example, Stream Processors, Inc. is provider **SPI\_PROVIDER\_SPI**.

Data type **spi\_provider\_t** identifies a provider. The Stream programming model defines the provider functions listed below; see *Stream Reference Manual* for details.

• **spi\_component\_get\_provider** Get the provider of a component

• SPI\_COMPONENT\_NEW Define a component, including its provider

• spi\_provider\_get\_name Get a provider name

• SPI\_SCHEDGROUP\_NEW Define a scheduling group, including its provider

• spi\_schedgroup\_register\_component Register a component with a scheduling group

# 4.3 Runtime reporting

## 4.3.1 Logs

The Stream programming model provides *logs* for runtime messages. Every component generates a debug log with log name **SPI\_LOG\_DEBUG** and an error log with log name **SPI\_LOG\_ERROR**. A component may define additional logs with **spi\_log\_new**.

A logging level controls the amount of logged information. The logging level is a 32-bit bitmask, called the *enable mask* of the log, so a program can control up to 32 independent logging levels for each log. By default, the SPM runtime disables all debug log levels, enables all error log levels, and intermixes timestamped output from all logs on **stdout**. The user can control log behavior with special SPM command-line options:

**--spi\_log\_dir**=*dir* specifies a log file directory,

--spi\_log\_mask=log,mask specifies an enable mask for a log, and --spi\_log\_timestamps=[0|1] disables or enables log entry timestamps.

The Stream programming model defines the logging functions listed below; see *Stream Reference Manual* for details.

spi\_get\_log

spi\_log

spi\_log\_get\_desc

spi\_log\_get\_enable\_mask

spi\_log\_get\_name

Get the log with a given name

Write a message to a log

Get the description of a log

Get the enable mask of a log

Get the name of a log

• spi log new Define a log

• spi\_log\_set\_enable\_mask Set the enable mask of a log

## **4.3.2 Timers**

The Stream programming model provides built-in *timers* to measure program performance. A component can also define additional timers with **spi\_timer\_new**. Timers measure execution time on stream processor hardware or on simulation with **sprun**. Timer measurements under the simulator are very accurate for DSP MIPS code and for long-running kernels, but can differ from hardware execution times for stream operations.

The Stream programming model includes several built-in timers:

- **SPI\_TIMER\_CMDHANDLER** measures the time spent in the command handler function of a component.

- **SPI\_TIMER\_EXECUTE** measures the time spent in the execute function of a component.

- SPI TIMER KERNEL measures the time spent in the most recently invoked kernel.

- SPI TIMER LOAD DSP measures the time required to load a DSP MIPS image.

- **SPI\_TIMER\_SPM** starts when the stream programming model runtime starts. The stream programming model runtime never stops this timer, so a program can use it to measure elapsed time since the runtime started.

- SPI\_TIMER\_STARTUP measures the startup time of the stream programming model runtime.

To reduce execution overhead, the SPM runtime updates **SPI\_TIMER\_CMDHANDLER** and **SPI\_TIMER\_EXECUTE** timers only in debug mode or in profile mode, not in release mode. It updates the other three built-in timers in all modes.

The Stream programming model defines the timer functions listed below; see Stream Reference Manual for details.

• **spi\_get\_time** Get the system time

spi\_get\_timer

spi\_timer\_get\_desc

spi\_timer\_get\_name

Get the timer with a given name

Get the description of a timer

Get the name of a timer

• **spi timer get nanoseconds** Get the elapsed time since a timer started

• **spi\_timer\_get\_start\_count** Get the number of times a timer has been started

• **spi\_timer\_get\_total\_nanoseconds** Get the total elapsed time of a timer

spi\_timer\_new

spi\_timer\_start

spi\_timer\_stop

Define a timer

Start a timer

Stop a timer

## 4.3.3 Tracing

Simulation of a program compiled in profile mode produces trace information, allowing the user to evaluate program performance with **spperf** or **spide**. The Stream programming model defines the program tracing functions listed below; see *Stream Reference Manual* for details.

• spi\_trace\_is\_enabled Check if tracing is enabled

spi\_trace\_startspi\_trace\_stopStart tracingStop tracing

#### 4.4 Initialization files

Instead of providing explicit code to create component instances, create connections between instances, and execute instance initialization commands for an application, a programmer can provide a high-level description of component instances, connections, and instance initialization commands in an *initialization file*. Initialization files can simplify the coding of SPM applications.

The user may specify initialization files at runtime by passing one or more **--spi\_init\_file** options to **spi\_spm\_start**. **spi\_spm\_start** processes initialization files in the order of the **--spi\_init\_file** options. It returns a failure status if it encounters any error while processing an initialization file. To see the cause of the failure, build a debug version of the executable (or of both System MIPS and DSP MIPS executables) with **spc -g.** Then pass option **--spi\_log\_mask=debug,1** to **spi\_spm\_start** to enable log level **SPI\_LOG\_LEVEL\_DEBUG** in the **SPI\_LOG\_DEBUG** log and examine the debug log to diagnose the cause of the failure.

**spi\_spm\_start** creates instances and connections described in the initialization files and executes initialization commands in the files in the given order. If any command receives a failing response error code (that is, any error code other than **SPI\_RESPONSE\_ERRNO\_OK**), **spi\_spm\_start** aborts initialization file processing and returns

failure status. The application can use **spi\_get\_instance** and **spi\_get\_connection** to get access to created instances and connections, as shown in the Example below.

## 4.4.1 Syntax

An initialization file is a sequence of statements using XML syntax. Each statement consists of a tag followed by one or more key/value pairs:

```

<tag key=value ... />

```

Here *tag* is one of **image**, **instance**, **connection**, or **command**; each is described below. Each *key* is a tag-specific name, and *value* gives the value for *key*. In keeping with XML syntax, each *value* should be quoted.

The initialization file may also include XML-style comments:

```

<!--This is a comment -->

```

Comments must be on a single line, but other XML statements in an initialization file may span multiple lines.

## 4.4.1.1 image

The **image** statement loads an image onto the DSP MIPs processor. Its format is:

```

<image target=pel file=pathname [ argv=arglist ] />

```

Here *pel* is **SPI\_PEL\_DSP\_MIPS** to specify the DSP MIPS processor and *pathname* gives the pathname of the executable image to be loaded to DSP MIPS. The optional **argv** key gives the argument list *arglist* for the target image. The *arglist* consists of whitespace-separated arguments, with single quotes to enclose an argument containing whitespace. For example,

#### 4.4.1.2 instance

The **instance** statement creates a new instance of a component and sets it to the running state. Its format is:

Here *name* gives the name of the new instance; the application can subsequently call **spi\_get\_instance**(*name*) to get the **spi\_instance\_t** handle of the instance. *component* gives the name of the component from which the instance is created. *provider* gives the component provider (for example, **SPI\_PROVIDER\_SPI**).

The remaining **instance** keys are optional. *schedgroup* specifies a scheduling group name to search for the component; **spi\_spm\_start** searches for *component* with **spi\_schedgroup\_component\_find** if this key is given, or with **spi\_component\_find** otherwise. *min* and *max* specify the required component version. *initial\_state* specifies the initial state of the component, with possible values "**paused**" and "**running**"; a new instance normally starts in the paused state.

#### 4.4.1.3 connection

The **connection** statement creates a connection between two previously created instances or between a previously created instance and the application. Its format is:

```

<connection name=name

depth=depth

[ from=instance:port ]

[ to=instance:port ] />

```

Here *name* gives the name of the new connection; the application can subsequently call **spi\_get\_connection**(*name*) to get the **spi\_connection\_t** handle of the connection. *depth* is the maximum number of buffers allowed in the connection at any one time. *instance* and *port* specify an instance name and port name to connect. If the **connection** statement specifies both **from** and **to** keys, **spi\_spm\_start** creates a connection in the same manner as **spi\_connect**. If the statement specifies only a **from** or a **to** key, **spi\_spm\_start** creates a connection between the application and an instance in the same manner as **spi\_connection\_new**.

#### 4.4.1.4 command

The **command** statement sends one or more commands to an instance. Its format is:

```

<command instance=name cmd=payload ... />

```

Here *name* gives the name of the instance to which the commands are sent. *cmd* is the name of a command: either a built-in command (for example, **SPI\_CMD\_START**), or the name of the command created by **spi\_cmd\_register** (for example, **FOO\_CMD\_DOIT**). *payload* is the payload associated with the *cmd*; for a command with no payload, *payload* must be "**null**" or "**NULL**".

#### 4.4.2 Example

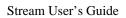

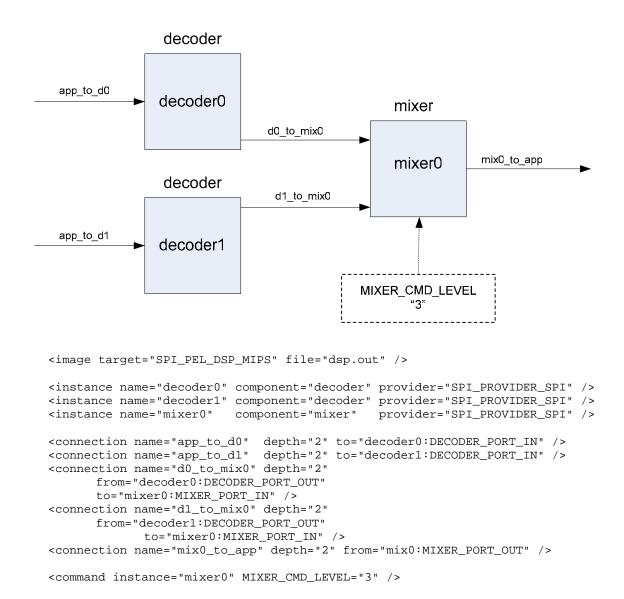

In this example, DSP MIPS image **dsp.out** contains two components, a decoder and a mixer. Component **decoder** has one input port **DECODER\_PORT\_IN** and one output port **DECODER\_PORT\_OUT**. Component **mixer** has one input port **MIXER\_PORT\_IN** and one output port **MIXER\_PORT\_OUT**. The mixer component defines command **MIXER\_CMD\_LEVEL** with an integer payload. The initialization file below creates two instances of **decoder** and one instance of **mixer**, connects the instances and the application, and sends a command to the mixer:

The application can use spi\_get\_connection to get a handle to the app\_to\_d0 connection and then use that connection to send a buffer to instance decoder0:

```

spi_connection_t app_to_d0_connection = spi_get_connection("app_to_d0");

spi_connection_push(app_to_d0_connection, buffer, -1);

```

Similarly, the application can use **spi\_get\_instance** to get a handle to the **mixer0** instance and then use that handle to send a command to the mixer:

```

spi_instance_t mixer0_inst = spi_get_instance("mixer0");

spi_response_t response = spi_cmd_send(mixer_inst, MIXER_CMD_LEVEL, 5, 0);

```

Section <u>Initialization file</u> of chapter <u>Demo Application spm\_demo</u> below provides a concrete example of the use of an initialization file in demo program **spm\_demo**.

# 5 Pipeline API

A kernel function running on the DPU cannot access Stream program data in DSP MIPS memory directly. The Stream programming model Pipeline API defines stream functions to load data from DSP MIPS memory to the lane register file (LRF) and to store data from the LRF to DSP MIPS memory, using efficient stream processor hardware instructions. These functions allow the Stream programming model to handle DSP MIPS / DPU data coherency issues (cache) automatically. The *Stream Reference Manual* chapter *Pipeline API* describes each Pipeline API function in more detail.

## 5.1 Streams

The DPU of a stream processor cannot access memory directly. Instead, it accesses data in the lane register file (LRF) of the processor. Stream programs represent LRF data as *streams* and use streams to pass data to and from kernel functions. A stream represents a fixed-length sequence of records of a given type in the LRF.

The <u>Pipeline API</u> chapter below describes DSP MIPS stream functions, including **spi\_load\_\*** and **spi\_store\_\*** functions that load stream data to the LRF and store stream data from the LRF. The <u>Kernel API</u> chapter below describes kernel stream functions, including **spi\_\*read** and **spi\_\*write** functions that read stream data from the LRF and write stream data to the LRF.

A Stream program may declare a stream only within a function (that is, as a local declaration); global stream declarations are not allowed. A stream declaration uses standard C syntax with one extension: the *size* of the stream in the LRF is specified in parentheses after the stream name:

```

stream int chicken(16); // a stream of 16 ints (one per lane on SP16)

```

The stream size indicates the number of records allocated in the LRF for this stream; it must be a compile time constant. The size gives the total number of data records for which LRF space is allocated, so each lane is allocated space for *size* / **SPI\_LANES** data records. Because of DPU hardware restrictions, the specified stream size must always be a multiple of **SPI\_LANES**.

A function that declares and uses streams is called a pipeline function. **spc** currently performs LRF allocation on a per-pipeline function basis, so a pipeline function may not call another pipeline function.

A stream declaration can specify an explicit LRF address (byte offset) in addition to a size:

```

stream int turkey(256, 1024); // a stream of 256 ints at LRF address 1024

```

This declares a stream of 256 words which begins at byte offset 1024 in the LRF. The offset must be a compile-time constant and a multiple of 4 \* **SPI\_LANES**. A program should not declare streams with explicit offsets that result in overlapping streams, as **spc** will not handle the aliasing of the streams correctly. In general, SPI discourages the use of stream declarations with explicit LRF address specifications.

The LRF is of limited size: it contains **SPI\_LRF\_SIZE** words per lane. On SP16 and SP8, **SPI\_LRF\_SIZE** is 4,096, so the LRF contains 256 Kbytes on SP16, 128 Kbytes on SP8. The total LRF space allocated by all streams "live" at any one time cannot exceed the size of the LRF. **spc** determines the "live" range of a stream in a program through analysis of stream use in the code. By default, **spc** tries to preserve parallelism between kernels and stream loads and stream stores. It searches backwards from each **spi\_load\_\*** to find the first preceding kernel, and then it allocates the LRF so that the load and the kernel can proceed in parallel if they are not data-dependent. Similarly, it searches forward from each **spi\_store\_\*** to find the first subsequent kernel, and then it allocates the LRF so that the store and the kernel can proceed in parallel if they are not data-dependent. If this algorithm results in overallocation of the LRF, **spc** issues a warning and attempts to allocate streams by reducing program parallelism. It

reports a compile time error if the LRF remains over-allocated. In this case, the programmer must reduce LRF use by reducing stream sizes.

By default, **spc** allocates 1 Kbyte per lane to hold local arrays for a kernel. Use the **local\_array\_size** pragma described <u>below</u> to change the default value for a kernel.

Stream stores records sequentially in memory, just like an array. For example, consider the following code:

```

typedef struct { int32x1 x, y, z; } xyz;

stream xyz my_stream(96);

spi_buffer_t buf;

...

spi_load_block(my_stream, buf, 0, 96);

```

Here **spi\_load\_block** loads 96 3-word records (288 words) of stream data from buffer **buf** into the LRF. If the data stored in **buf** is record **r[0]** through record **r[95]**, then the records are stored in **my\_stream** in the LRF as follows:

| Word:   | 0      | 1      | 2      | 3      | 4      | 5      | <br>285     | 286     | 287     |

|---------|--------|--------|--------|--------|--------|--------|-------------|---------|---------|

| Member: | r[0].x | r[0].y | r[0].z | r[1].x | r[1].y | r[1].z | <br>r[95].x | r[95].y | r[95].z |

| Record: |        | r[0]   |        |        | r[1]   | ·      | <br>•       | r[95]   |         |

Stream stores multibyte data in littleendian format; the diagram above does not show individual bytes.

## 5.1.1 Restrictions

Because streams are used for transferring data to a kernel function running on the DPU, stream data record types must be constructed from DPU basic types. User-defined structured stream data types may only contain DPU basic types. Stream code cannot assign to streams, use streams in expressions, use pointers to streams, or use arrays of streams.

#### For example:

The table below provides additional detail on the use of various Stream types.

|                                |                                                                                   | Declare | in contex       | ts                     | Derived types   |              |           |          |            |           |

|--------------------------------|-----------------------------------------------------------------------------------|---------|-----------------|------------------------|-----------------|--------------|-----------|----------|------------|-----------|

| Туре                           | Example(s+)                                                                       | ပ       | Kernel argument | inline kernel argument | Inside a kernel | Struct field | Vector of | Array of | Pointer to | Stream of |

| DPU basic type                 | int8x4                                                                            | Yes     | Yes             | Yes                    | Yes             | Yes          | Yes       | Yes      | Yes        | Yes       |

| Other basic type               | char                                                                              | Yes     | -               | -                      | -               | Yes          | -         | Yes      | Yes        | -         |

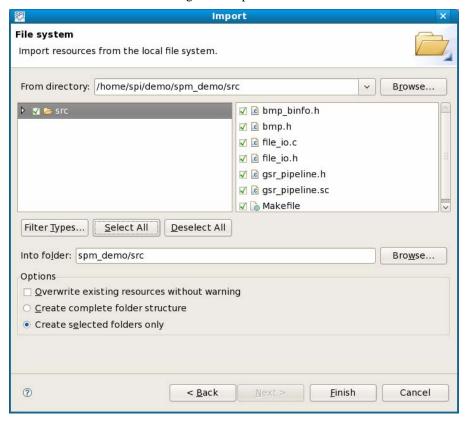

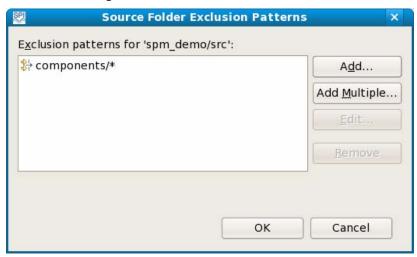

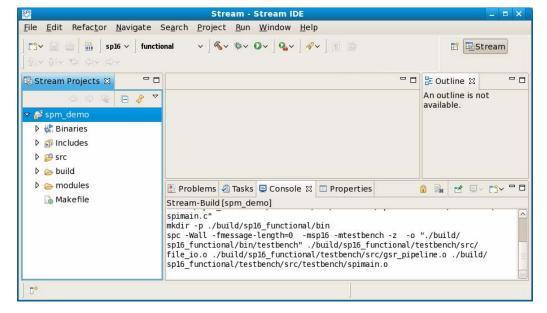

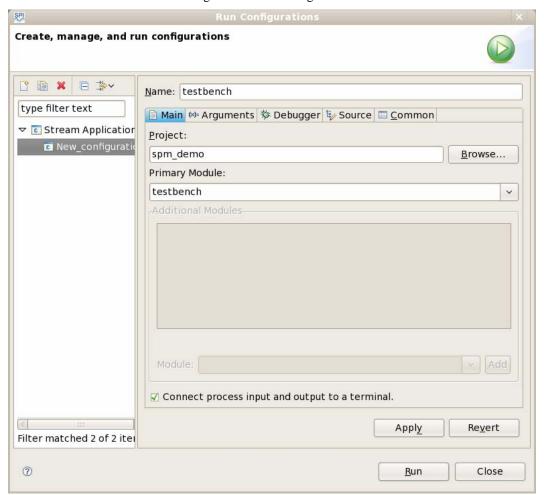

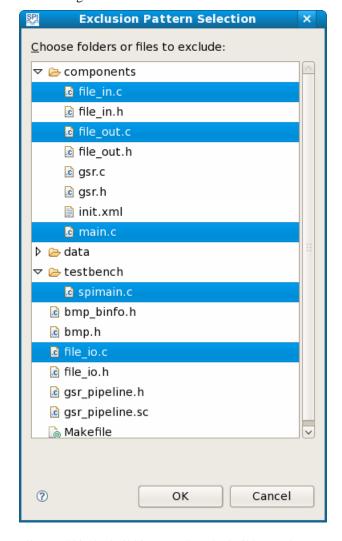

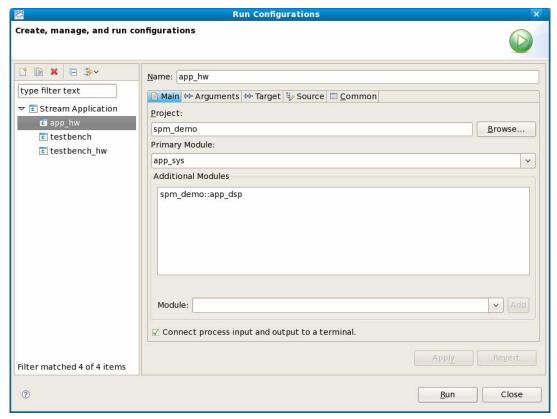

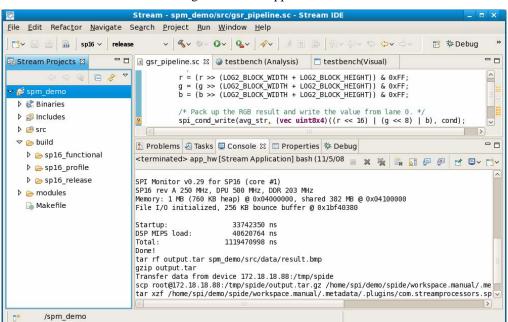

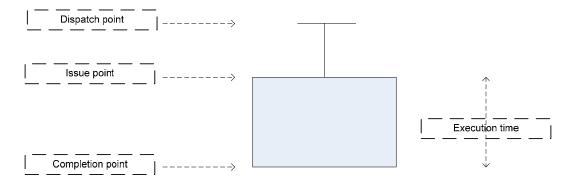

| Struct of only DPU basic types | <pre>struct {   int8x4 x; }</pre>                                                 | Yes     | -               | Yes                    | Yes             | Yes          | Yes       | Yes      | Yes        | Yes       |